2.5D packaging technology: when is it worth the added cost

As chiplet design pushes performance limits, 2.5D Packaging technology is gaining attention for its balance of bandwidth, integration, and manufacturability. But when do its benefits truly justify the added cost? For decision-makers evaluating Thermal Management solutions, IC Testing equipment, Power Conversion efficiency, and Supply Chain Resilience strategies, this article explains where 2.5D packaging creates measurable value across advanced semiconductor and Industrial IoT solutions.

When does 2.5D packaging solve a real business problem?

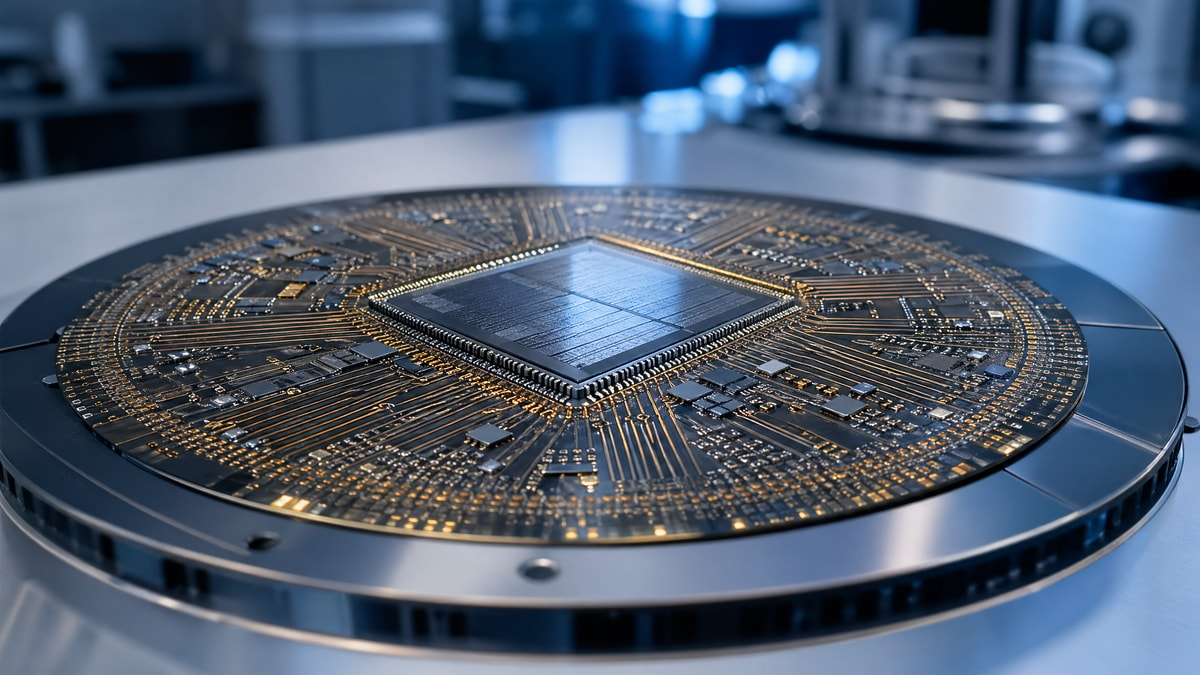

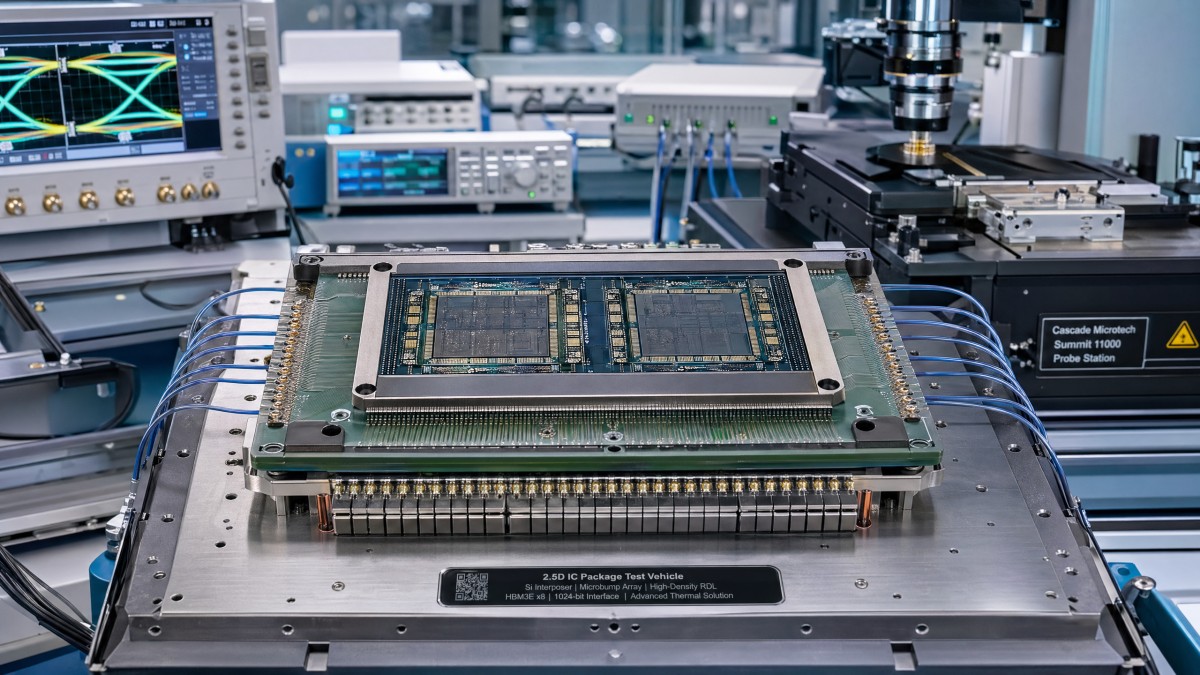

2.5D packaging places multiple dies side by side on an interposer, usually silicon, glass, or an advanced organic substrate, to create dense interconnects without fully stacking active dies as in 3D IC. For engineering teams, the value proposition is straightforward: higher bandwidth than conventional multi-chip packages, shorter signal paths than board-level integration, and lower design risk than many vertical stack options. For procurement and business teams, however, the question is not technical novelty but whether these gains produce measurable return within a 2–5 year product window.

The added cost becomes easier to justify when the system bottleneck is no longer transistor density alone but data movement, thermal path control, package footprint, or heterogeneous integration. Typical triggers include AI accelerators, high-speed networking ASICs, edge inference modules, radar processing, industrial vision, and power-dense control systems that need logic, memory, analog, and sensor functions in one compact architecture. In these cases, 2.5D packaging often reduces board complexity even when the package itself costs more.

For information researchers and technical evaluators, one practical way to think about 2.5D packaging is to compare the cost premium against three operational constraints: bandwidth per watt, space per function, and integration risk across multiple die nodes. If at least 2 of these 3 constraints are already limiting product roadmap execution, the discussion should move beyond package unit price and into total platform economics.

This is where G-SSI offers strategic value. By benchmarking advanced packaging, testing, thermal behavior, and supply-chain readiness against SEMI-aligned manufacturing discipline, AEC-Q100 reliability expectations where relevant, and ISO/IEC 17025 test rigor, G-SSI helps teams judge whether a 2.5D architecture is technically justified, commercially viable, and operationally supportable across cross-border manufacturing environments.

What 2.5D packaging improves most clearly

- Interconnect density: short, fine-pitch links can support much higher die-to-die bandwidth than board traces or standard package routing.

- Heterogeneous integration: different process nodes can be combined, such as advanced logic with mature-node analog, RF, or memory.

- Form factor efficiency: package area may still be large, but system board area often shrinks by 20%–40% in integration-heavy designs.

- Signal integrity: shorter paths can improve latency control and reduce loss in high-speed interfaces, especially in memory-centric architectures.

Which applications justify the added cost faster?

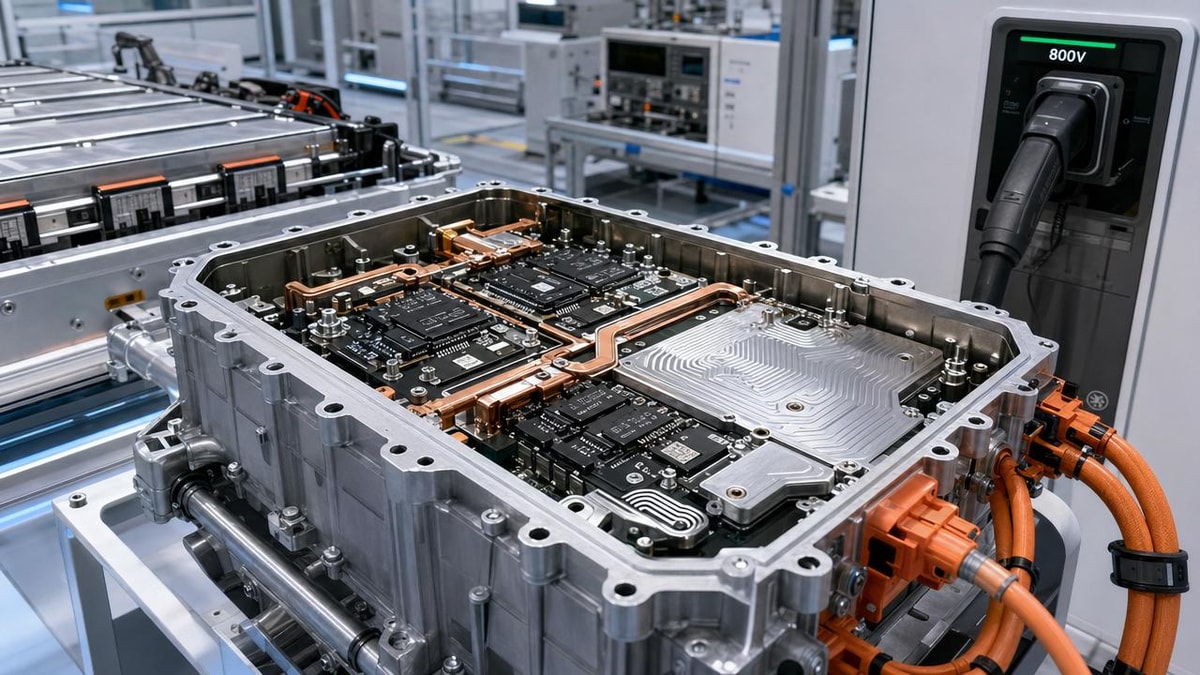

Not every product benefits equally from 2.5D packaging. In many industrial and commercial systems, conventional flip-chip BGA, fan-out, or multi-chip module approaches remain more economical. The strongest justification appears where bandwidth demand and package-level integration are both critical, and where the product margin can absorb a more complex assembly and test flow. That is why adoption often starts in infrastructure, compute, automotive-adjacent sensing, aerospace electronics, and premium industrial control.

For project managers and sourcing teams, the key is to rank applications by penalty of underperformance. If missing a latency target, thermal target, or board-space target causes downstream redesign, qualification delay, or enclosure change, then the initial package premium may be lower than the cost of system compromise. In practical programs, a 6–12 month redesign cycle can outweigh a package cost increase if product launch timing is commercially sensitive.

The table below maps common application profiles to decision logic. It is not a universal rulebook, but it helps align engineering, purchasing, and management around the same threshold questions before engaging packaging suppliers, OSAT partners, or test houses.

A common pattern emerges: 2.5D packaging is most defensible when it removes a system-level penalty, not when it simply improves a laboratory metric. G-SSI typically advises customers to examine 4 decision layers in sequence: architecture fit, thermal budget, testability, and supply continuity. Skipping any one of these can turn an elegant package concept into a costly qualification problem.

Scenarios where conventional packaging may remain better

If the product ships in high volume with aggressive unit-cost pressure, requires modest data rates, and can tolerate larger board area, advanced substrate-based packaging or fan-out may deliver a better cost-performance ratio. The same applies when field serviceability matters more than peak integration density, or when the organization lacks mature package co-design and thermal validation workflows.

Distributors and channel partners should also note that not all customer segments are ready for the ecosystem demands of 2.5D packaging. Lead-time variability, more specialized test coverage, and tighter process control requirements can complicate forecasting. In many cases, the right commercial move is to position 2.5D as a roadmap option for premium SKUs rather than a baseline package strategy across the whole portfolio.

How does 2.5D packaging compare with 3D, fan-out, and conventional MCM?

Comparison is where many evaluations become clearer. 2.5D packaging sits between standard multi-chip integration and true 3D stacking. It can offer much of the interconnect advantage needed for chiplet systems without forcing the thermal and yield complexity that often comes with vertically stacked active dies. That does not make it automatically cheaper than 3D or fan-out in every program, but it often produces a more manageable engineering trade-off.

For quality and safety managers, the comparison should include inspectability and failure analysis, not just performance. Interposer-based architectures can simplify some signal and integration issues while introducing new concerns around warpage, assembly alignment, thermal cycling stress, and package-level yield. Reliability planning therefore needs to begin early, typically during package-architecture selection rather than after prototype tape-out.

The table below summarizes common decision differences across four packaging routes. The exact outcome always depends on die size, I/O count, power density, and target volume, but this framework helps non-design stakeholders participate in technical-commercial decisions with more confidence.

The most important takeaway is that 2.5D packaging is rarely a stand-alone winner. It wins relative to alternatives when it best balances 3 competing needs: performance uplift, qualification manageability, and supply-chain practicality. G-SSI’s cross-pillar view is especially useful here because advanced packaging decisions are inseparable from testing capability, thermal materials, electronic chemicals, and fabrication-environment control.

A quick comparison checklist

- If your design needs very high die-to-die I/O in a 1-package architecture, shortlist 2.5D packaging early.

- If vertical thermal extraction is already difficult at prototype stage, treat 3D stacking with caution.

- If product margin is tight and board area is available, advanced substrate or MCM may remain the better business choice.

- If supplier concentration is a major risk, compare packaging routes not only by unit cost but by qualified ecosystem breadth over 12–24 months.

What should buyers and evaluators check before approving a 2.5D program?

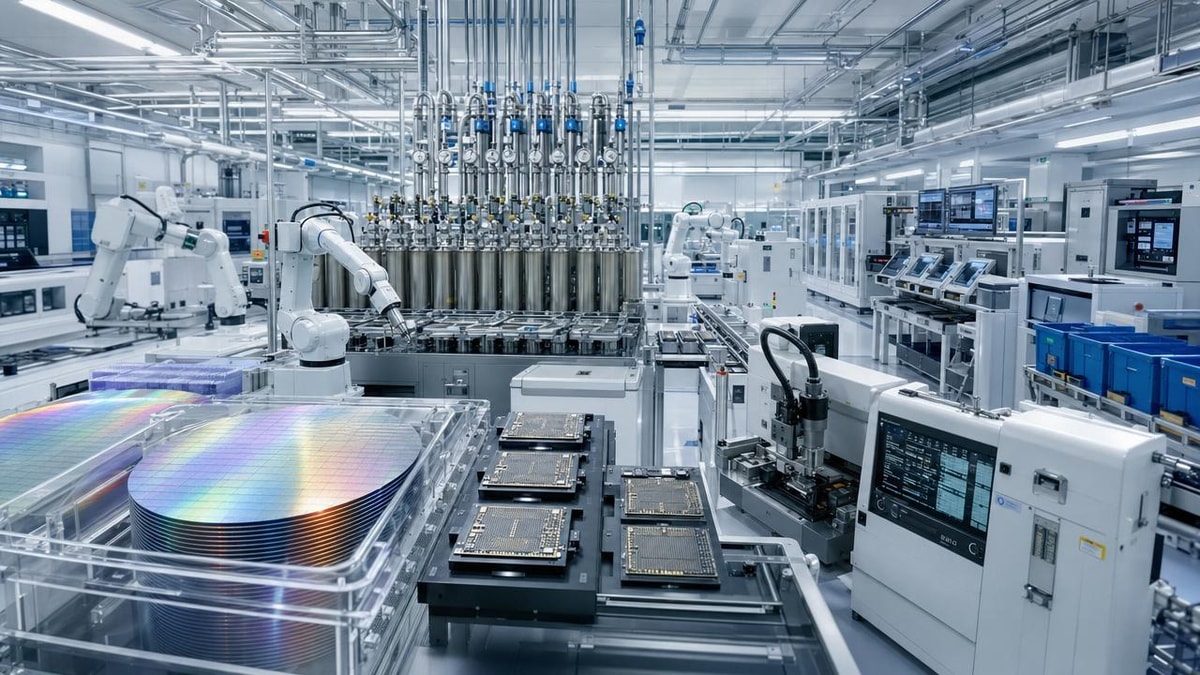

For purchasing teams, the biggest mistake is evaluating 2.5D packaging through the lens of package quote alone. The real cost base includes interposer choice, assembly complexity, test insertion strategy, thermal interface design, substrate availability, reliability qualification, and engineering iteration count. A lower quote can become expensive if it creates retest loops, slows NPI by 4–8 weeks, or narrows second-source options.

Technical evaluators should require a decision package that covers at least 5 key checkpoints: die-to-die bandwidth target, package power density, thermal path definition, known-good-die strategy, and test coverage plan. For industrial and infrastructure products with long service life, teams should also ask whether package architecture supports stable requalification if one die node or one OSAT route changes during the product lifecycle.

The procurement guide below is designed for cross-functional review. It helps align R&D, sourcing, quality, and commercial stakeholders before volume planning, especially when lead times may range from 8–16 weeks depending on interposer flow, substrate readiness, and test resource availability.

In practice, the best buying decision usually comes from a staged approval model. Stage 1 screens architecture fit. Stage 2 validates prototype thermals and test escape risk. Stage 3 checks volume readiness, including alternate sourcing and qualification evidence. This 3-stage model reduces premature commitment and gives executives clearer approval gates tied to commercial milestones.

A practical 4-step internal review flow

- Define the bottleneck in measurable terms, such as bandwidth, latency, board area, or power-density target.

- Compare 2.5D packaging with at least 2 alternatives using the same cost and risk assumptions.

- Validate whether thermal management and IC testing plans are mature enough for first-pass qualification.

- Approve only after supply-chain resilience, sample schedule, and change-control responsibilities are documented.

Where G-SSI adds value during evaluation

G-SSI supports buyers and engineering teams by connecting package architecture decisions to upstream and downstream realities: semiconductor process compatibility, package and test infrastructure, thermal management materials, environmental control, and reliability measurement discipline. This matters because a 2.5D packaging decision is not isolated. It affects yield assumptions, test cost, power-conversion efficiency at system level, and even the acceptable purity and process control of packaging-related materials across the manufacturing chain.

What risks, misconceptions, and standards should not be ignored?

One common misconception is that 2.5D packaging is automatically the most future-ready option for chiplet design. In reality, future readiness depends on ecosystem maturity and change tolerance. If your program expects frequent die revisions, multiple sourcing transfers, or phased regional manufacturing, the package architecture must support those transitions without excessive requalification burden. A technically elegant package can still be a poor strategic choice if it locks the product into a fragile supply network.

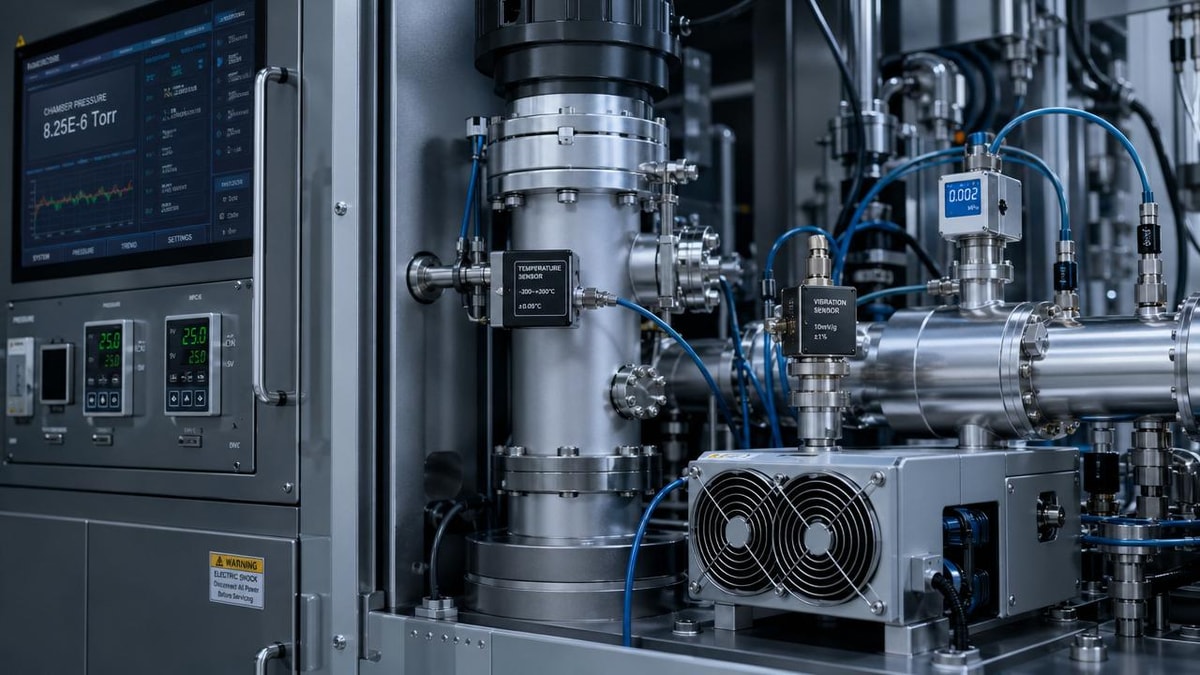

Another misconception is that thermal challenges can be solved late. In 2.5D packaging, thermal behavior is linked to interposer choice, die placement, underfill behavior, lid and heat spreader design, and package-to-board interaction. Teams should establish thermal simulation and physical correlation early, ideally before full prototype spin. A delay of even 1 validation cycle, often 3–6 weeks, can create compounded schedule pressure across test, reliability, and customer sampling.

Standards and compliance also matter. Depending on target market, teams may align reliability plans with AEC-Q100 style thinking for automotive-adjacent electronics, use SEMI-oriented process discipline in manufacturing environments, and rely on ISO/IEC 17025 principles for test-lab credibility and repeatability. These are not marketing labels. They shape how data is generated, reviewed, and trusted during supplier qualification and customer approval.

Frequent risk points in 2.5D packaging projects

- Underestimating package-level thermal density and discovering hotspot concentration after layout freeze.

- Assuming known-good-die coverage is sufficient without matching it to final package test conditions.

- Treating interposer and substrate lead times as commodity items during volume ramp planning.

- Ignoring reliability stress alignment between end-use environment and qualification plan.

FAQ for evaluators and buyers

Is 2.5D packaging only for high-end AI chips?

No. AI is a major driver, but not the only one. 2.5D packaging can also make sense in industrial vision, sensor fusion, networking, aerospace electronics, and compact infrastructure modules where multiple dies need high-speed proximity. The threshold is not the market label; it is whether the system gains enough from bandwidth, integration density, or board simplification to justify the extra package and validation effort.

What delivery timeline should buyers expect?

There is no single universal timeline, but evaluation and sourcing should assume a more structured flow than standard packaging. Early feasibility and supplier alignment may take 2–4 weeks, engineering sample planning another 4–8 weeks, and qualification cycles often extend further depending on thermal, reliability, and test complexity. Any program that needs rapid launch should clarify sample, pilot, and mass-production milestones at the start.

What is the most overlooked cost in 2.5D packaging?

Often it is not the interposer itself but the cumulative cost of yield learning, advanced test insertion, and schedule slips caused by incomplete thermal or reliability planning. In B2B environments, one delayed qualification window can affect customer approval, inventory planning, and contract timing more severely than the visible package cost premium.

How should distributors position 2.5D packaging to end customers?

Position it as a solution for specific performance-density bottlenecks, not as a universal upgrade. Customers respond better when the conversation focuses on system impact: bandwidth limits, thermal zoning, package footprint, mixed-node integration, and supply-chain planning. This creates a more realistic sales path and reduces mismatch between technical ambition and procurement readiness.

Why work with G-SSI when evaluating 2.5D packaging?

2.5D packaging decisions cut across architecture, manufacturing, testing, thermal management, materials control, and long-term sourcing. G-SSI is built for exactly this type of cross-functional decision. Our institutional focus on advanced packaging and testing, power semiconductors, industrial-grade sensors, high-purity electronic materials, and semiconductor environment control allows us to evaluate the package not as an isolated component, but as part of a sovereign-grade digital infrastructure strategy.

For CTOs, IC design leaders, sourcing managers, and quality teams, we can support evaluation in several practical ways: parameter confirmation for chiplet and interposer architecture, packaging route comparison, thermal management review, IC testing strategy alignment, sample feasibility discussion, and supply-chain resilience screening. This helps teams shorten decision cycles and reduce misalignment between R&D targets and procurement realities.

If you are reviewing a 2.5D packaging program, contact us with 3 core inputs: target application, die integration plan, and expected qualification timeline. We can then help you assess whether the added package cost is justified, what alternatives deserve comparison, what standards should frame the evaluation, and which risks should be addressed before RFQ, sample build, or volume commitment.

You can consult us for package architecture screening, test and reliability checkpoints, delivery-cycle expectations, customization pathways, standards alignment, sample support discussions, and quotation communication priorities. That way, your team moves from abstract interest in 2.5D packaging to a decision grounded in measurable performance value, realistic manufacturability, and resilient supply execution.

- Power Semiconductors

- Electronic Chemicals

- Thermal Management

- Data Fidelity

- Industrial IoT

- Power Conversion

- Supply Chain Resilience

- Environment Control

- Industrial-Grade Sensors

- IC Testing

- 2.5D Packaging

- Digital Infrastructure

- Industrial IoT solutions

- Supply Chain Resilience strategies

- IC Testing equipment

- Power Conversion efficiency

- 2.5D Packaging technology

- Thermal Management solutions

Get weekly intelligence in your inbox.

No noise. No sponsored content. Pure intelligence.