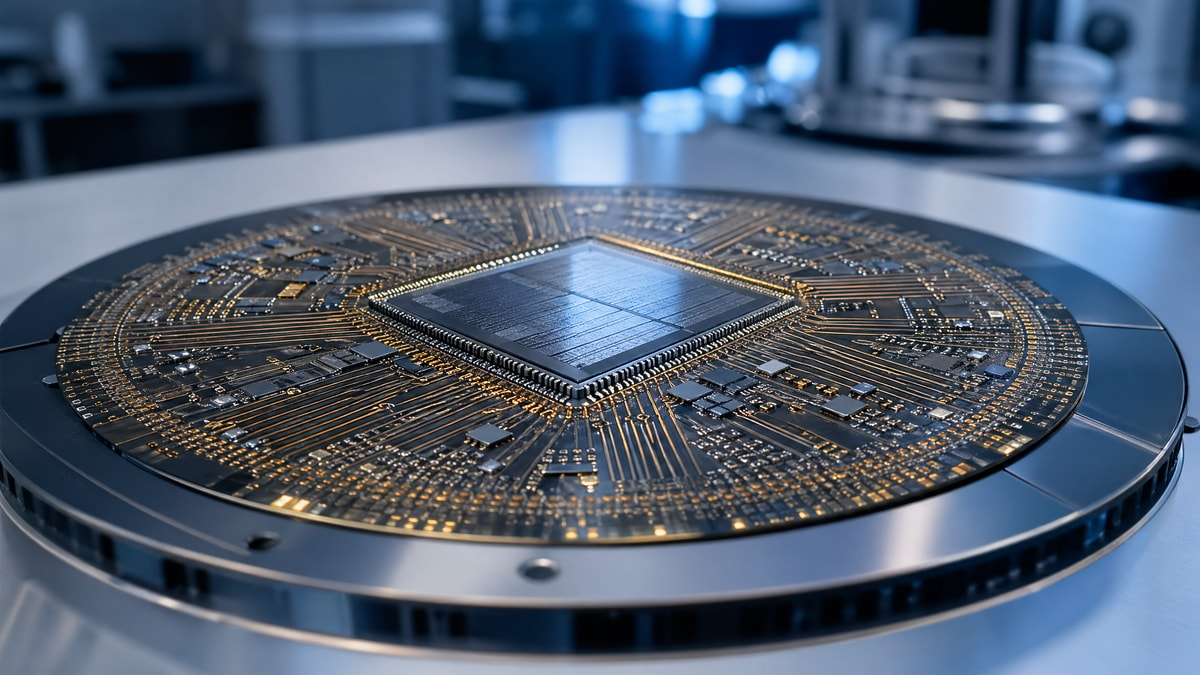

What Can Go Wrong in Fan-out Wafer Level Pkg?

Fan-out wafer level packaging can unlock higher I/O density and thinner form factors, but it also introduces risks in thermal management, IC testing, and long-term reliability. For leaders in Semiconductor Fabrication, Industrial IoT, and Autonomous Systems, understanding what can go wrong is essential to protecting data fidelity, supply chain resilience, and the performance of smart sensors and advanced 2.5D packaging strategies.

Why does fan-out wafer level packaging fail in real projects?

Fan-out wafer level packaging, often shortened to FOWLP, solves several integration problems at once: it can reduce package thickness, improve electrical performance through shorter interconnects, and support higher I/O counts than many traditional package formats. Yet the same design freedoms that make fan-out attractive also create new failure paths during reconstitution, redistribution layer formation, molding, singulation, assembly, and field operation.

In practice, what goes wrong in fan-out wafer level packaging is rarely a single defect. Failures often emerge through a chain of 3 to 5 linked issues, such as die shift during reconstitution, RDL stress accumulation, thermal mismatch between mold compound and silicon, and incomplete test coverage at wafer level. For technical evaluators and quality teams, this means package risk must be assessed as a system problem rather than a one-step process check.

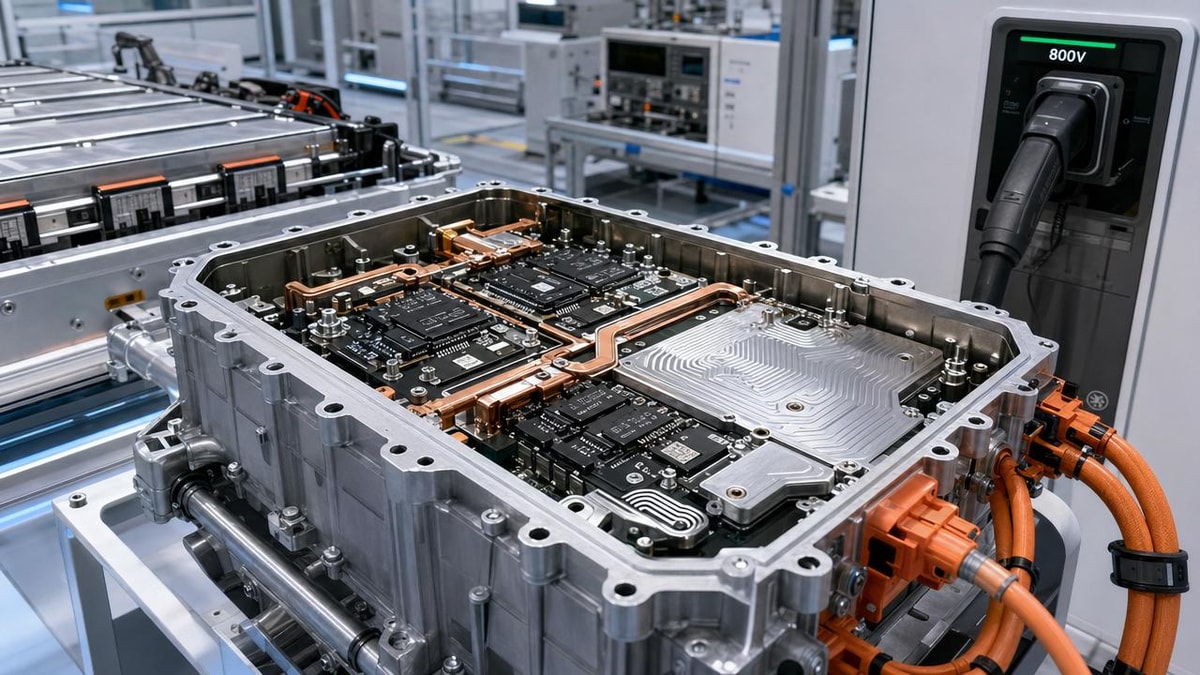

This matters even more for industrial-grade MEMS, power devices, edge AI modules, and sensor interface chips used in autonomous systems. These applications often operate across extended temperature ranges, repeated thermal cycling, and long service intervals measured in 5 to 10 years. A packaging shortcut that appears acceptable in early qualification can become a field reliability issue when exposed to vibration, humidity, or sustained current loading.

At G-SSI, benchmarking is valuable because fan-out packaging must be judged not only by density and miniaturization, but also by reliability, thermal behavior, testability, and supply chain controllability. That perspective helps CTOs, sourcing leaders, and industrial IoT architects avoid decisions based only on package profile or short-term unit cost.

The most common failure categories

- Die shift and placement deviation during reconstitution, which can reduce overlay margin and distort downstream RDL alignment windows.

- RDL cracking, delamination, or via failure caused by warpage, thermal mismatch, or local stress concentration around die edges.

- Package warpage that interferes with probe contact, assembly yield, board attach quality, and final coplanarity performance.

- Hidden thermal bottlenecks that degrade power handling, sensor stability, or high-speed signal integrity over continuous operating cycles.

Which process steps create the highest technical risk?

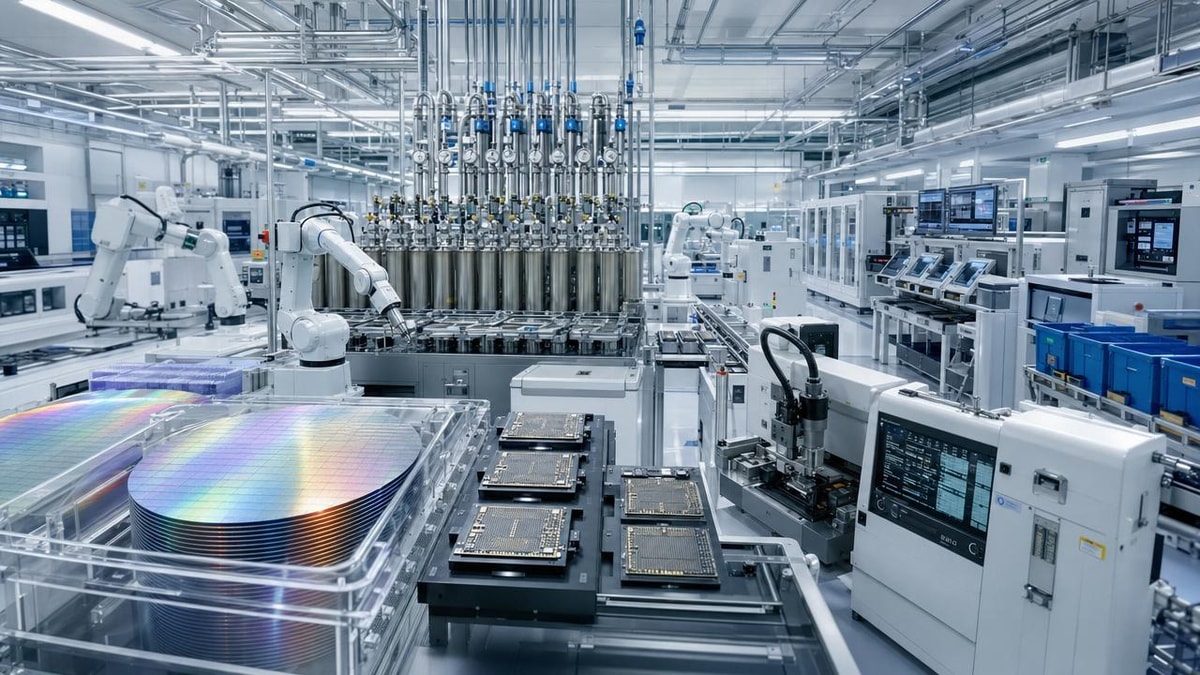

The highest-risk stages in fan-out wafer level packaging usually appear before the final package looks defective. Reconstitution is one such stage. Once known-good dies are embedded into a reconstructed wafer or panel, any die placement variation can propagate into redistribution and bumping operations. Even small positional drift can narrow process windows, especially when line and space targets move into finer geometries and multi-layer RDL stacks are required.

RDL formation is another major risk point. Copper redistribution lines must survive both process stress and use-case stress. In industrial and automotive-adjacent applications, thermal cycling intervals can range from hundreds to thousands of cycles depending on the qualification plan. If dielectric integrity, adhesion, or via geometry are not robust, failure may not appear during initial electrical test, but can emerge later as intermittent opens or resistance drift.

Mold compound selection also deserves more scrutiny than many sourcing teams expect. A mismatch in coefficient of thermal expansion, modulus, or moisture sensitivity can increase package warpage and interfacial stress. For thin packages, where total thickness may be compressed into a narrow design envelope, the tolerance for stress imbalance becomes even smaller. This is one reason why package thinning and higher density should always be reviewed together, not as independent improvements.

Testing is the final technical risk amplifier. Wafer-level and package-level test strategies do not always capture the same faults. In fan-out architectures, probing access, thermal conditions, and stress screening logic may leave gaps if the qualification plan is built around conventional assumptions. For enterprise buyers, this means the test flow should be reviewed as a design-for-quality issue, not just a production cost line item.

Where failures often begin

1. Reconstitution and die placement

Placement accuracy, die rotation, and mold flow behavior determine whether later routing layers remain within alignment budget. In advanced layouts, a process window can tighten rapidly when die counts increase or edge clearance shrinks.

2. RDL and dielectric stack-up

The number of RDL layers, copper thickness, dielectric modulus, and via geometry all affect fatigue performance. A package intended for continuous operation at elevated junction temperatures needs a different margin strategy than one serving low-duty consumer logic.

3. Warpage and assembly interaction

Warpage is not only a packaging metric. It affects test contact, substrate attach, underfill behavior where used, and board-level reliability. Reviewing warpage only at room temperature is often insufficient; teams should compare behavior across multiple thermal points in the expected process and use profile.

How do major failure modes compare for engineering and procurement teams?

A structured comparison helps decision-makers move beyond generic statements about yield or reliability. The table below summarizes common fan-out wafer level packaging failure modes, where they typically originate, how they show up during evaluation, and why they matter to technical, commercial, and quality stakeholders.

For sourcing and program management teams, the key lesson is that each failure mode affects more than yield. A die shift issue can delay qualification by 2 to 4 weeks if mask or routing revisions are needed. A warpage issue can force changes in assembly setup, handling, or board process windows. The financial impact often appears later than the technical trigger.

The next step is to evaluate whether a given supplier can control these risks consistently across lot size, package thickness, and application class. High-density mobile logic, industrial sensor modules, and power-adjacent mixed-signal devices do not share the same stress profile, so supplier claims should be tested against the actual operating environment.

G-SSI supports this by framing advanced packaging as a benchmarking problem: material behavior, thermal management, test escape risk, and long-term reliability should be reviewed together. That approach is especially relevant when organizations compare China-based mature-node expansion with stricter international expectations for process stability and quality traceability.

What procurement teams should ask before approval

- What are the control limits for die placement, warpage, and RDL integrity, and are they tracked lot by lot?

- Which failure mechanisms were screened through electrical test, thermal cycling, moisture exposure, and board-level verification?

- How does the package behave across low-volume sampling, pilot runs, and volume production ramps?

- What changes in material set, process flow, or subcontract handling would trigger requalification?

What should buyers and quality teams evaluate before selecting a fan-out package strategy?

Selection should begin with use-case clarity. A compact wearables package, an industrial sensor node, and an edge compute controller can all use fan-out packaging, but the risk priorities differ. In many B2B reviews, teams overfocus on I/O density and footprint reduction while underweighting test access, field thermal load, and supply chain resilience. That imbalance often leads to avoidable qualification loops.

A practical selection model uses 5 core dimensions: electrical performance, thermal path quality, mechanical reliability, test coverage, and manufacturing continuity. If the package is intended for harsh-environment electronics, a sixth dimension should be added: environmental durability under humidity, vibration, or repetitive thermal shock. This framework helps technical and commercial stakeholders speak with the same decision logic.

The table below provides a procurement-oriented checklist that can be used during RFQ review, supplier comparison, or design gate approval. It is especially useful when a project must balance thin form factor goals with reliability requirements linked to industrial IoT, smart sensors, or long-life infrastructure electronics.

This checklist is not only for procurement. It gives quality managers a clear set of audit points and helps business evaluators compare offers that may look similar at the quote level. A lower initial package price can become more expensive if it adds 1 extra qualification loop, tighter storage controls, or a longer debug cycle after board assembly.

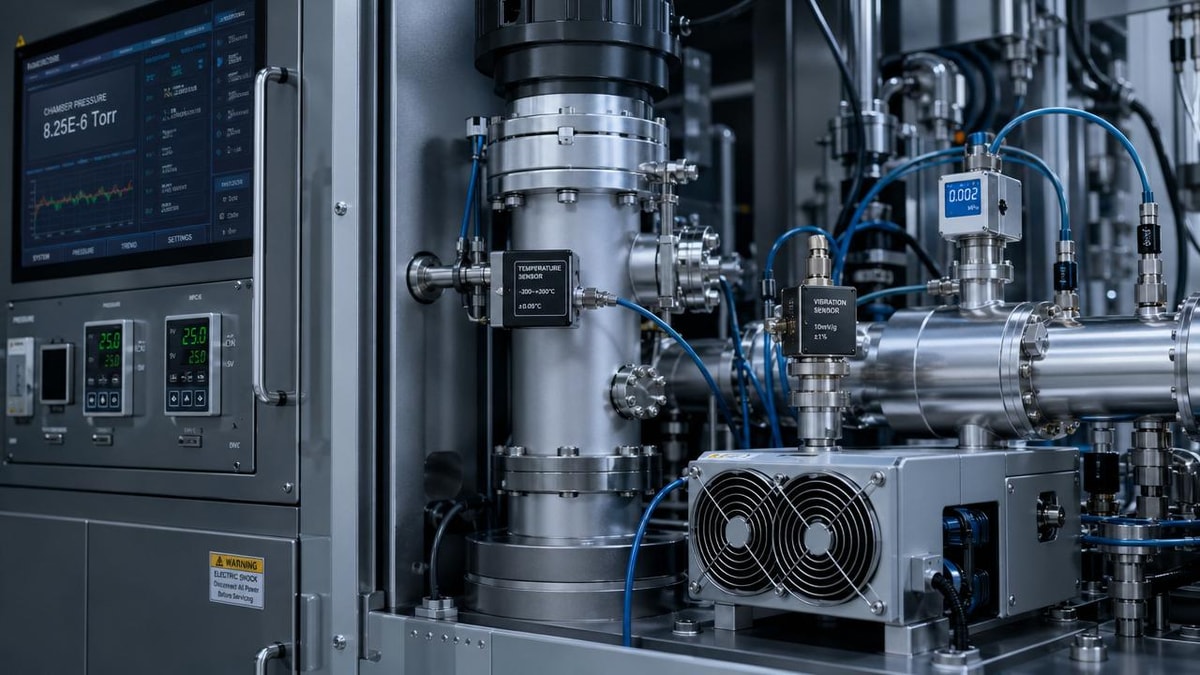

For advanced packaging reviews, G-SSI emphasizes alignment with practical standards and verification discipline. Depending on the target market, teams may need to map expectations to frameworks commonly used in semiconductor reliability, automotive-grade evaluation, clean measurement practice, or lab traceability, such as SEMI, AEC-Q100, and ISO/IEC 17025-linked test environments.

A 4-step selection workflow

- Define the real operating profile: temperature range, duty cycle, mechanical stress, and service-life target.

- Screen package architecture options against thermal path, I/O demand, and board assembly compatibility.

- Review supplier process controls, qualification evidence, and change management triggers.

- Run pilot validation through sample build, electrical screening, and reliability checks before volume lock-in.

Which standards, test practices, and misconceptions deserve attention?

One common misconception is that a fan-out package that passes early electrical test is already low risk. In reality, electrical pass data is only one layer of evidence. Many critical packaging issues are thermo-mechanical and emerge over time. For industrial and infrastructure applications, reliability confidence should be built through multiple screens rather than a single acceptance point.

Another misconception is that thinner always means better. Thinner packages can improve product design freedom, but they also reduce mechanical margin. If package thickness, die size, and mold properties are not well matched, the result may be increased warpage or stress concentration. Decision-makers should ask whether the package target was set by system need or by a marketing-driven miniaturization goal.

Standards and qualification frameworks matter because they create discipline around test conditions, sampling logic, and traceable interpretation. Depending on the application, teams may review temperature cycling, high-temperature storage, moisture sensitivity, board-level reliability, and failure analysis routines. The right qualification plan is usually staged across development, pilot, and release phases rather than compressed into one final gate.

For organizations building sovereign digital infrastructure, sensor networks, or high-efficiency power systems, this staged approach reduces hidden exposure. It also aligns better with the G-SSI perspective that semiconductor packaging is part of a wider reliability architecture involving fabrication integrity, environment control, data fidelity, and traceable test methodology.

FAQ: practical questions from research and sourcing teams

How do I know if fan-out wafer level packaging is suitable for my product?

It is suitable when you need a compact footprint, improved electrical routing, and higher I/O density without a conventional substrate burden. However, suitability should be confirmed against 3 checks: thermal load, reliability target, and assembly compatibility. If your device faces long-duration industrial operation or repeated thermal cycling, qualification depth becomes more important than package size alone.

What should I prioritize during supplier evaluation?

Prioritize process control evidence, not only datasheet claims. Review die placement control, warpage monitoring, RDL reliability strategy, and test escape prevention. For serious programs, ask for change notification rules, pilot validation flow, and the expected timeline from sample build to qualification, which commonly spans several weeks rather than a few days.

Are fan-out packages always better than substrate-based advanced packages?

No. Fan-out excels in many compact and high-integration scenarios, but substrate-based options may offer better fit for some thermal, routing, or large-die integration needs. The better choice depends on package size, I/O architecture, power density, and board-level reliability targets. Comparison should be application-led, not trend-led.

What lead-time and validation risks should commercial teams expect?

Commercial teams should account for sample preparation, pilot build, reliability screening, and any design iteration that follows early findings. In many complex packaging programs, one design correction can add 2 to 4 weeks. Planning should also include material availability, subcontract coordination, and the possibility of requalification if process conditions materially change.

Why work with G-SSI when evaluating fan-out wafer level packaging risk?

G-SSI is positioned for organizations that need more than a general packaging summary. Our focus is the intersection of semiconductor fabrication integrity, advanced packaging and testing, smart sensor reliability, high-purity process support, and controlled manufacturing environments. That cross-domain view is valuable when fan-out wafer level packaging decisions affect not only product form factor, but also thermal stability, test confidence, and supply chain resilience.

For CTOs, IC design directors, industrial IoT architects, sourcing teams, and quality leaders, we help structure evaluation around measurable questions. These include package architecture fit, thermal management assumptions, qualification scope, standards alignment, pilot validation priorities, and supplier comparison logic. This is especially relevant when projects involve mature-node manufacturing expansion paired with international reliability expectations.

You can contact G-SSI to discuss concrete topics such as fan-out package risk mapping, advanced packaging selection, test and reliability review priorities, sample evaluation planning, expected qualification checkpoints, and cross-comparison with 2.5D or other integration paths. If your team is balancing technical risk against procurement timeline, we can also help define the key decision gates before RFQ closure or pilot release.

If you are currently assessing what can go wrong in fan-out wafer level packaging, the most useful next step is a focused review of your use case: device type, thermal load, package constraints, test strategy, target standards, and delivery schedule. Reach out with your parameter questions, package selection challenges, certification concerns, sample support needs, or quotation requirements, and we can help frame a decision path grounded in reliability, manufacturability, and long-term infrastructure confidence.

Get weekly intelligence in your inbox.

No noise. No sponsored content. Pure intelligence.